# High Efficiency 2-Channel LED Backlight with Flash Function

#### **Features**

- Wide input range: 2.7V~5.5V

- High efficiency step-up 2-Channel LED driver

- 2-Ch current sinks, up to 8-LEDs per string

- ▶ Up to 29.8mA/Ch in backlight mode and up to 59.6mA/Ch in flash mode

- ► +/-0.6% current matching at 20.2mA

- ▶ +/-1.5% current accuracy at 20.2mA

- I2C/PWM dual dimming control scheme

- ► 11-bit I<sup>2</sup>C exponential or linear mapping with programmable transition ramp time

- Wide range PWM dimming with programable transition ramp time

- 100Hz to 100kHz frequency

- 0.2% to 100% duty cycle at 20kHz

- Programmable current sink turn on/off ramp time and shape

- Selectable boost converter switching frequency 1MHz or 500kHz with 20% shift up option

- Programmable input PWM hysteresis to minimize jitter at low PWM duty cycle

- Programmable OVP (25.9V/32V) and current limit (2.6A/1.8A)

- Programmable flash current and timeout

- LED open/short protection

- Status reporting through I<sup>2</sup>C interface

## **Applications**

Smartphone/Tablet Backlight and Selfie Flash

### **Brief Description**

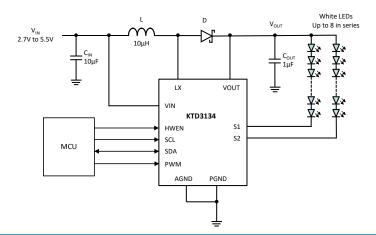

KTD3134 is the ideal power solution for LED backlighting and selfie flash in medium to large size LCD panels. It is a highly integrated step-up DC-DC converter operating with an input voltage from 2.7V to 5.5V, accommodating 1-cell lithium ion batteries or 5V supply. It includes a high voltage power NMOS, as well as two current sinks, resulting in a simpler and smaller solution with fewer external components. High switching frequency allows the use of a smaller inductor and capacitor.

Each of the two regulated current sinks can regulate up to 29.8mA in backlight mode. With a maximum of 32V at the output of the step-up converter, each string can connect up to 8-LED in series for a 16-LED application.

KTD3134 is equipped with I<sup>2</sup>C interface for various controls. For additional flexibility, PWM dimming with wide range frequency and duty cycle is included to support Content Adaptive Brightness Control (CABC).

KTD3134 also adds selfie flash function to the existing backlight solution by boosting the sink current up to 59.6mA/Ch and integrating a flash timeout of up to 1.5sec.

Various protection features are built into KTD3134, including cycle-by-cycle inductor current limit protection, output overvoltage protection, LED fault (open or short) protection and thermal shutdown protection.

KTD3134 is available in a RoHS compliant 12-ball 1.19mm  $\times$  1.64mm WLCSP or a 16-lead 3mm  $\times$  3mm  $\times$  0.75mm Thin-QFN package.

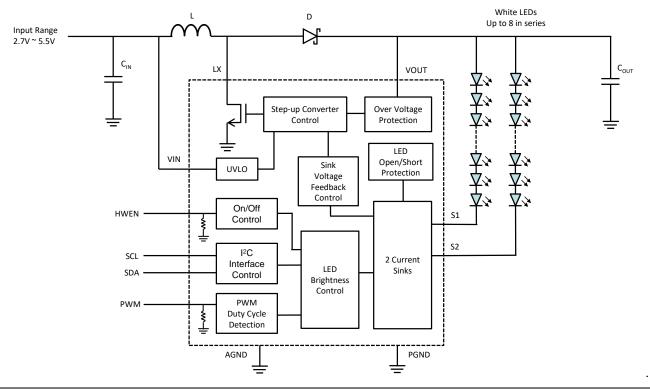

## Typical Application

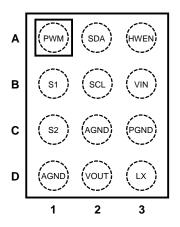

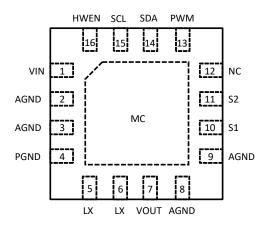

## **Pin Description**

| Piı      | n #        | Name | Function                                                                                                   |

|----------|------------|------|------------------------------------------------------------------------------------------------------------|

| WLCSP-12 | TQFN33-16  |      |                                                                                                            |

| A1       | 13         | PWM  | PWM dimming input pin. There is an internal $400k\Omega$ pull-down resistor at this pin to GND.            |

| A2       | 14         | SDA  | Bi-directional data pin of the I <sup>2</sup> C interface.                                                 |

| А3       | 16         | HWEN | Active high hardware enable pin. There is an internal $400 k\Omega$ pull-down resistor at this pin to GND. |

| B1       | 10         | S1   | Regulated output current sink #1.                                                                          |

| B2       | 15         | SCL  | Clock input pin of the I <sup>2</sup> C interface.                                                         |

| В3       | 1          | VIN  | Input supply pin for the IC.                                                                               |

| C1       | 11         | S2   | Regulated output current sink #2.                                                                          |

| C2, D1   | 2, 3, 8, 9 | AGND | Analog ground pin.                                                                                         |

| С3       | 4          | PGND | Power ground pin.                                                                                          |

| D2       | 7          | VOUT | Output voltage sense pin of the step-up converter.                                                         |

| D3       | 5, 6       | LX   | Switching pin of the step-up converter.                                                                    |

|          | MC         |      | Metal chassis. Connect to ground for electrical and thermal usage. MC is internally connected to AGND pin. |

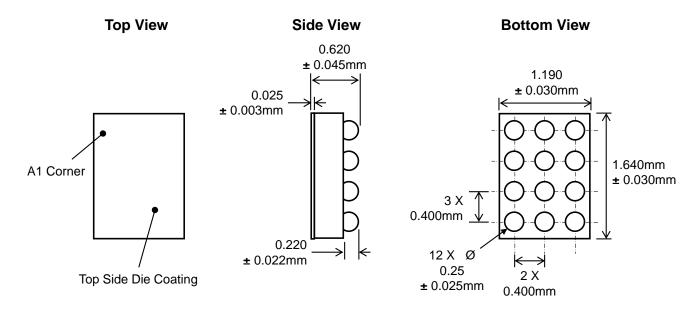

#### WLCSP-12

Top View

TOP VIEW TOP VIEW

12-Bump 1.19mm x 1.64mm x 0.62mm WLCSP Package

#### **Top Mark**

WW = Device ID Code = LI

XX = Date Code, YY = Assembly Code

ZZZZ = Serial Number

#### **TQFN33-16**

Top View

16-Lead 3mm x 3mm x 0.75mm TQFN Package

#### **Top Mark**

XX = Device Code YY = Date Code, Z = Assembly Code

# Absolute Maximum Ratings<sup>1</sup>

#### $(T_A = 25^{\circ}C \text{ unless otherwise noted})$

| Symbol              | Description                                      | Value           | Units |

|---------------------|--------------------------------------------------|-----------------|-------|

| VIN                 | Input Voltage                                    | -0.3 to 6       | V     |

| LX, VOUT            | High Voltage Nodes                               | -0.3 to 35      | V     |

| S1, S2              | High Voltage Nodes                               | -0.3 to 22      | V     |

| SCL, SDA, PWM, HWEN | Control Pins                                     | -0.3 to VIN+0.3 | V     |

| TJ                  | Junction Operating Temperature Range             | -40 to 150      | °C    |

| Ts                  | Storage Temperature Range                        | -65 to 150      | °C    |

| TLEAD               | Maximum Soldering Temperature (at leads, 10 sec) | 300             | °C    |

| ESD                 | HBM Electrical Static Discharge                  | 2.0             | kV    |

## Thermal Capabilities<sup>2</sup>

| Symbol              | Description                                        | Value | Units |

|---------------------|----------------------------------------------------|-------|-------|

| WLCSP-12            |                                                    |       |       |

| θја                 | Thermal Resistance – Junction to Ambient           | 89    | °C/W  |

| P <sub>D</sub>      | Maximum Power Dissipation at T <sub>A</sub> ≤ 25°C | 1410  | mW    |

| ΔΡ <sub>D</sub> /ΔΤ | Derating Factor Above T <sub>A</sub> = 25°C        | -11.3 | mW/°C |

| TQFN33-16           |                                                    |       |       |

| θја                 | Thermal Resistance – Junction to Ambient           | 42    | °C/W  |

| PD                  | Maximum Power Dissipation at T <sub>A</sub> ≤ 25°C | 2976  | mW    |

| ΔΡ <sub>D</sub> /ΔΤ | Derating Factor Above T <sub>A</sub> = 25°C        | 23.8  | mW/°C |

## **Ordering Information**

| Part Number   | Marking <sup>3</sup> | Operating Temperature | Package   |

|---------------|----------------------|-----------------------|-----------|

| KTD3134EUS-TR | LIXXYYZZZZ           | -40°C to +85°C        | WLCSP-12  |

| KTD3134EFJ-TR | LIYYZ                | -40°C to +85°C        | TQFN33-16 |

April 2019 - Revision 04a Page 3 Company Confidential

Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. Functional operation at conditions other than the operating conditions specified is not implied. Only one Absolute Maximum rating should be applied at any one time.

<sup>2.</sup> Junction to Ambient thermal resistance is highly dependent on PCB layout. Values are based on thermal properties of the device when soldered to an EV board.

<sup>3. &</sup>quot;XXYYZZZZ" / "YYZ" are the date code, assembly code and serial number / the date code and assembly code.

## Electrical Characteristics<sup>4</sup>

Unless otherwise noted, the *Min* and *Max* specs are applied over the full operation temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C, while *Typ* values are specified at room temperature (25°C).  $V_{IN} = 3.6$ V.

| Symbol                 | Description                          | Conditions                                                  | Min  | Тур  | Max  | Units |

|------------------------|--------------------------------------|-------------------------------------------------------------|------|------|------|-------|

| IC Supply              |                                      |                                                             |      |      |      |       |

| V <sub>IN</sub>        | Input operating range                |                                                             | 2.7  |      | 5.5  | V     |

| UVLO                   | Input under voltage lockout          | Rising edge                                                 |      | 2.45 | 2.65 | V     |

| UVLO <sub>HYST</sub>   | UVLO hysteresis                      |                                                             |      | 0.05 |      | V     |

| ΙQ                     | IC operating V <sub>IN</sub> current | Switching                                                   |      | 1.9  |      | mA    |

| Ishdn                  | IC shutdown V <sub>IN</sub> current  | Vin = 5.5V, HWEN = GND                                      |      | 0.5  |      | μΑ    |

| I <sub>SB</sub>        | IC standby V <sub>IN</sub> current   | Standby, V <sub>IN</sub> = 4.2V,<br>HWEN = SDA = SCL = 1.8V |      | 7    |      | μΑ    |

| Step-Up C              | onverter                             |                                                             |      |      |      |       |

| R <sub>DS(ON)</sub>    | NMOS on-resistance                   |                                                             |      | 0.2  |      | Ω     |

| I <sub>LIM</sub>       | Peak NMOS current limit              | Default setting                                             |      | 2.6  |      | Α     |

| Fsw                    | Oscillator frequency                 | Default setting                                             |      | 1.0  |      | MHz   |

| D <sub>MAX</sub>       | Maximum duty cycle                   | FSW = 1MHz                                                  |      | 94   |      | %     |

| V <sub>OVP</sub>       | OVP threshold                        | Default setting                                             |      | 32   |      | V     |

| Current Si             | nk                                   |                                                             |      |      |      |       |

|                        |                                      | Current setting = 1mA, T <sub>A</sub> = 25°C                | -4   |      | 4    | %     |

|                        | Output current accuracy              | Current setting = 20.2mA, T <sub>A</sub> = 25°C             | -1.5 |      | 1.5  | %     |

| Laure                  |                                      | Current setting = 59.6mA, T <sub>A</sub> = 25°C             | -3.5 |      | 3.5  | %     |

| Isink                  |                                      | Current setting = 1mA, T <sub>A</sub> = 25°C                | -1.2 |      | 1.2  | %     |

|                        | Output current matching <sup>5</sup> | Current setting = 20.2mA, T <sub>A</sub> = 25°C             | -0.8 |      | 0.8  | %     |

|                        |                                      | Current setting = 59.6mA, T <sub>A</sub> = 25°C             | -0.6 |      | 0.6  | %     |

| Vsov                   | Current sink over voltage threshold  |                                                             |      | 12   |      | V     |

| TFAULT                 | Current sink fault delay             |                                                             |      | 6    |      | μs    |

| T <sub>TIMEOUT</sub>   | Flash timeout                        | Default setting                                             |      | 500  |      | ms    |

| Logic Con              | trol                                 |                                                             |      |      |      |       |

| V <sub>TH-L</sub>      | HWEN/PWM logic low threshold         |                                                             |      |      | 0.4  | V     |

| V <sub>TH-H</sub>      | HWEN/PWM logic high threshold        |                                                             | 1.4  |      |      | V     |

| F <sub>PWM</sub>       | PWM dimming frequency                |                                                             | 0.1  |      | 100  | kHz   |

| T <sub>PWM_ON</sub>    | PWM on time                          |                                                             | 0.1  |      |      | μs    |

| T <sub>PWM_OFF</sub>   | PWM off pulse low width              |                                                             | 20   |      |      | ms    |

| R <sub>Pull-Down</sub> | HWEN/PWM pull down resistors         |                                                             |      | 400  |      | kΩ    |

April 2019 - Revision 04a Page 4 Company Confidential

<sup>4.</sup> KTD3134 is guaranteed to meet performance specifications over the  $-40^{\circ}$ C to  $+85^{\circ}$ C operating temperature range by design, characterization and correlation with statistical process controls.

<sup>5.</sup> The current matching among channels is defined as  $|I_{SINK}-I_{AVG}|_{MAX}/I_{AVG}$ .

## **Electrical Characteristics<sup>6</sup>**

| Symbol                | Description                                                   | Conditions      | Min | Тур | Max | Units |  |

|-----------------------|---------------------------------------------------------------|-----------------|-----|-----|-----|-------|--|

| I <sup>2</sup> C-Comp | I <sup>2</sup> C-Compatible Voltage Specifications (SCL, SDA) |                 |     |     |     |       |  |

| VIL                   | Input Logic Low Threshold                                     |                 |     |     | 0.4 | V     |  |

| ViH                   | Input Logic High Threshold                                    |                 | 1.4 |     |     | V     |  |

| $V_{OL}$              | SDA Output Logic Low                                          | $I_{SDA} = 3mA$ |     |     | 0.4 | V     |  |

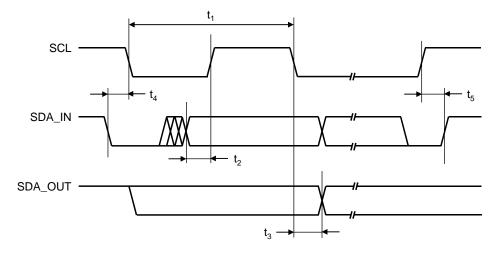

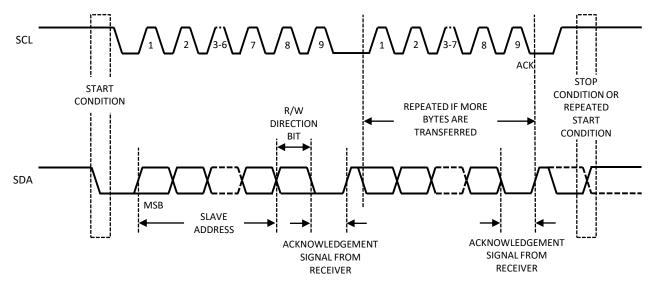

| I <sup>2</sup> C-Com  | patible Timing Specifications (SCL, SDA), see Figu            | ure 1           |     |     |     |       |  |

| t <sub>1</sub>        | SCL clock period                                              |                 | 2.5 |     |     | μs    |  |

| $t_2$                 | Data in setup time to SCL high                                |                 | 100 |     |     | ns    |  |

| <b>t</b> 3            | Data out stable after SCL low                                 |                 | 0   |     |     | ns    |  |

| t <sub>4</sub>        | SDA low setup time to SCL low (Start)                         |                 | 100 |     |     | ns    |  |

| <b>t</b> 5            | SDA high hold time after SCL high (Stop)                      |                 | 100 |     |     | ns    |  |

| Thermal               | Shutdown                                                      |                 |     |     |     |       |  |

| Тл-тн                 | IC thermal shutdown threshold                                 |                 |     | 150 |     | °C    |  |

| I J-TH                | IC thermal shutdown hysteresis                                |                 |     | 15  |     | °C    |  |

Figure 1. I<sup>2</sup>C Compatible Interface Timing

April 2019 - Revision 04a Page 5 Company Confidential

<sup>6</sup> KTD3134 is guaranteed to meet performance specifications over the  $-40^{\circ}$ C to  $+85^{\circ}$ C operating temperature range by design, characterization and correlation with statistical process controls.

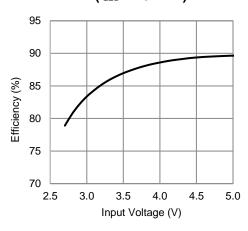

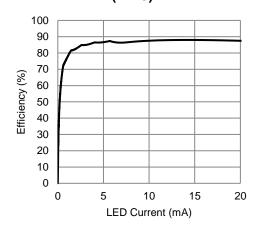

$V_{IN}=3.6V$ , 2P7S LEDs,  $I_{LED}=20.2mA$ ,  $L=10\mu H$  (Murata LQH3NPN100MJR),  $C_{IN}=10\mu F$ ,  $C_{OUT}=1\mu F$ ,  $I^2C$  register default settings, Temp = 25°C unless otherwise specified.

# LED Driver Efficiency vs. VIN (I<sub>LED</sub> = 20.2mA)

#### **Operating Current (Switching)**

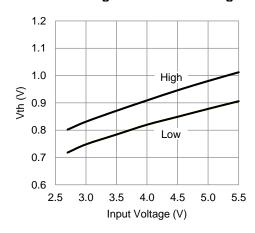

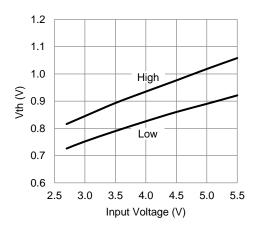

## **HWEN Logic Threshold Voltage**

# LED Driver Efficiency vs. LED Current (2P7S)

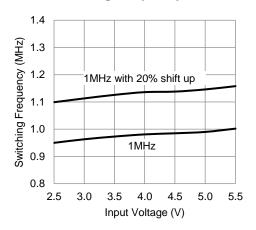

#### Switching Frequency vs. VIN

#### **PWM Logic Threshold Voltage**

$V_{IN}=3.6V$ , 2P7S LEDs,  $I_{LED}=20.2mA$ ,  $L=10\mu H$  (Murata LQH3NPN100MJR),  $C_{IN}=10\mu F$ ,  $C_{OUT}=1\mu F$ ,  $I^2C$  register default settings, Temp = 25°C unless otherwise specified.

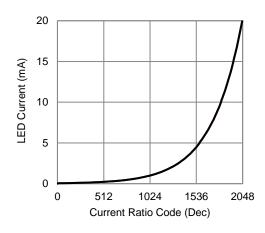

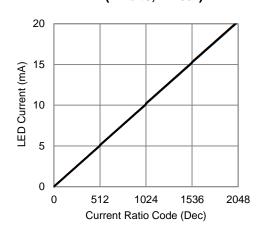

# LED Current vs. Current Ratio Code (11 bits, Exponential)

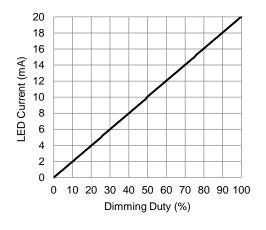

#### LED Current vs. PWM Duty Cycle (20kHz)

# LED Current vs. Current Ratio Code (11 bits, Linear)

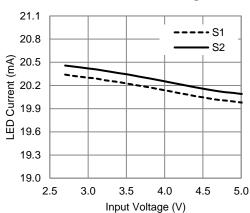

#### **LED Current Line Regulation**

$V_{IN}=3.6V$ , 2P7S LEDs,  $I_{LED}=20.2mA$ ,  $L=10\mu H$  (Murata LQH3NPN100MJR),  $C_{IN}=10\mu F$ ,  $C_{OUT}=1\mu F$ ,  $I^2C$  register default settings, Temp = 25°C unless otherwise specified.

100ms / div

100ms / div

$V_{IN}=3.6V$ , 2P7S LEDs,  $I_{LED}=20.2mA$ ,  $L=10\mu H$  (Murata LQH3NPN100MJR),  $C_{IN}=10\mu F$ ,  $C_{OUT}=1\mu F$ ,  $I^2C$  register default settings, Temp = 25°C unless otherwise specified .

## **Functional Block Diagram**

## **Functional Description**

KTD3134 is a unique current regulated step-up (boost) converter. Two current sinks are integrated to drive 2 strings of LEDs with good current matching and accuracy.

The voltage step-up is accomplished by a boost topology, using an inductor-based DC-DC switching converter, in which the inductor serves as an energy storage device in the system. Unlike a traditional DC-DC boost converter with a fixed output voltage, the KTD3134 dynamically changes its output voltage depending on the load. The use of unique control schemes maintains accurate current regulation in each of the two current sinks while leaving the output voltage at a minimum, increasing the overall conversion efficiency. The internal step-up converter dynamically controls the voltage at the output high enough to drive the LED string with the highest total forward voltage.

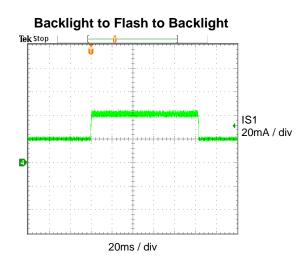

In additional to the normal backlight control function, KTD3134 also adds the selfie flash function by boosting sink current to a higher level with the flash timeout protection.

#### **Hardware Enable & Standby Mode**

KTD3134 has a logic input HWEN pin to enable/disable the device. When HWEN is set low, the device goes into shutdown mode, all I<sup>2</sup>C registers are reset to default, and the I<sup>2</sup>C interface is disabled. Under this condition, the device does not respond to any I<sup>2</sup>C command. Even when SCL/SDA's pull up voltage is much less than VIN voltage, it will not cause any extra leakage current.

When HWEN is set high, the device goes into standby mode, the  $I^2C$  interface is enabled, and the device can respond to  $I^2C$  command. Under this condition, if SCL/SDA's pull up voltage is much less than VIN voltage, it can cause a small leakage current. For example, if VIN = 4.2V and SCL/SDA's pull up voltage is 1.8V, there will be around  $7\mu A$  additional leakage current from VIN in this standby mode.

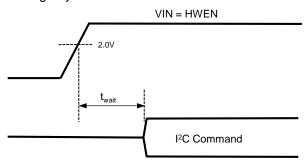

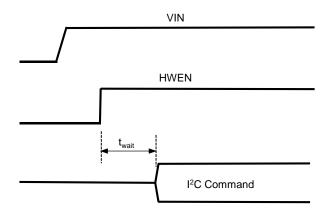

Based on HWEN's connection, there are two kinds of power-up sequences, shown in Figure 2 and Figure 3.

If HWEN is tied to VIN, once VIN goes above around 2.0V, HWEN should stay high for at least t<sub>wait</sub> = 150 μs time before any I<sup>2</sup>C command can be accepted.

April 2019 - Revision 04a Page 10 Company Confidential

If HWEN is driven by a GPIO, once HWEN goes from low to high, HWEN should stay high for at least twait = 150μs time before receiving any I<sup>2</sup>C command.

Figure 2. Power Up Sequence with HWEN Tied to VIN

Figure 3. Power Up Sequence with HWEN Driven by GPIO

Either HWEN input or I<sup>2</sup>C command can be used to turn off the part, but there are some differences.

- If setting HWEN input low to turn off the part, the LED current will be turned off immediately without any ramp down control. After that, the I<sup>2</sup>C interface is disabled.

- If using an I<sup>2</sup>C command to turn off backlight/flash mode while keeping HWEN high, the LED current will have ramp down control. After the LED current ramp down is finished, the I<sup>2</sup>C interface is still alive waiting for new command.

#### **Backlight & Flash Modes**

Once HWEN is set high, I<sup>2</sup>C Mode Register 0x02 Bits[1:0] (see Table 6) should be used to enable/disable backlight mode or flash mode. Bit[0] enables/disables backlight mode, and Bit[1] enables/disables flash mode. If Bits[1:0] is set as '11', Bit[1] has higher priority over Bit[0], so it works in flash mode. Once flash timeout is done, Bit[1] is reset to '0' automatically, then Bit[0] decides the mode.

#### **Backlight Full-scale LED Current**

The backlight mode's full-scale LED current I<sub>LED\_FS</sub> is defined as the LED current in backlight mode when PWM dimming duty cycle D<sub>PWM</sub> is 100% and the LED current ratio RATIO<sub>LED</sub> is also 100%. I<sub>LED\_FS</sub> is programmed by the Mode Register 0x02 Bits[7:3] (see Table 6). Full scale current ranges from 5mA to 29.8mA with 0.8mA/step and 20.2mA as the default.

#### **Backlight PWM Dimming**

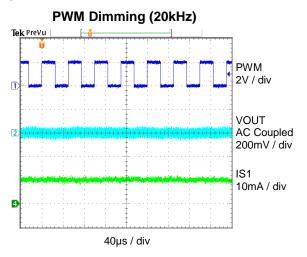

In backlight PWM mode, the input PWM duty cycle is converted internally to produce a DC output sink current (not pulsing). Backlight PWM dimming can be enabled or disabled by the PWM Register 0x06 Bit[7] (see Table 10), with enabled as default. When PWM is disabled, KTD3134 uses 100% as the dimming duty cycle for sink current calculation. When PWM is enabled, it can be programmed as either active high or active low by PWM Register 0x06 Bit[6], with active high as default. When PWM dimming is enabled, KTD3134 uses internal 20MHz sampling clock to detect the PWM duty cycle. It is recommended to have the minimum PWM on time as 0.1 µs.

April 2019 - Revision 04a Page 11 Company Confidential

For the example of 20kHz dimming frequency, the PWM duty cycle range can be 0.2%~100%. The PWM dimming frequency range can be as wide as 100Hz to 100kHz. When the input PWM duty cycle has a sudden change, there is a programmable transition ramp time controlled by Register 0x08 Bits[6:4] to make the LED current change smoother. For flash mode, the current is not related to the input PWM duty cycle.

#### **Backlight PWM Hysteresis**

In backlight mode, if PWM dimming frequency is high and PWM dimming duty cycle is low, even the internal fast 20MHz sampling clock's sampling error can be sufficient to cause the output LED current jitter. KTD3134 implements PWM hysteresis control to minimize the jitter. It can be programmed by PWM Register 0x06 Bits[5:3] (see Table 10). The input PWM duty cycle is converted to an internal 11-bit digital value, this PWM hysteresis decides how many LSBs of this 11-bit digital value is changed before the output LED current can follow the change. When PWM duty cycle changes in the same direction, no hysteresis exists. Only when the PWM duty cycle's change starts to go in different direction, does the hysteresis starts to take effect, and only when the change is larger or equal to the number of LSBs programmed, the output LED current starts to follow the change. Table 1 shows the relationship between the minimum LSB(s) and the PWM duty cycle hysteresis. Table 2 summarizes PWM Register 0x06 Bits[5:3]'s minimum setting to prevent jitter under different input PWM frequency conditions. The drawback of setting PWM hysteresis too high is that the output current becomes less accurate due to the hysteresis.

**Table 1. PWM Hysteresis**

| PWM Register<br>0x06 Bits[5:3] | Minimum LSB(s) | PWM Duty Cycle<br>Hysteresis |  |  |  |

|--------------------------------|----------------|------------------------------|--|--|--|

| 000                            | 0              | 0/2047 = 0%                  |  |  |  |

| 001                            | 2              | 2/2047 = 0.10%               |  |  |  |

| 010                            | 4              | 4/2047 = 0.20%               |  |  |  |

| 011                            | 6              | 6/2047 = 0.29%               |  |  |  |

| 100                            | 8              | 8/2047 = 0.39%               |  |  |  |

| 101                            | 10             | 10/2047 = 0.48%              |  |  |  |

| 110                            | 12             | 12/2047 = 0.59%              |  |  |  |

| 111                            | 14             | 14/2047 = 0.68%              |  |  |  |

Table 2. Register 0x06 Bits[5:3]'s Minimum Setting

| PWM Dimming<br>Frequency (kHz) | Sampling Error | Register 0x06 Bits[5:3]'s Minimum Setting to Prevent Jitter |

|--------------------------------|----------------|-------------------------------------------------------------|

| 0.1                            | 0.0005%        | 001                                                         |

| 1                              | 0.005%         | 001                                                         |

| 5                              | 0.025%         | 001                                                         |

| 10                             | 0.05%          | 001                                                         |

| 20                             | 0.1%           | 010                                                         |

| 40                             | 0.2%           | 011                                                         |

| 100                            | 0.5%           | 110                                                         |

#### **Backlight LED Current**

The LED current is always a DC current. It can be programmed for either exponential mapping mode or linear mapping mode by Register 0x03 Bit[1]. These two modes determine the transfer characteristic of dimming code to LED current. It also has 11-bit control, including the 8-bit MSBs from LED Current Ratio MSB Register 0x05 Bits[7:0] (see Table 9) and the 3-bit LSBs from LED Current Ratio LSB Register 0x04 Bits[2:0] (see Table 8). If only 8-bit dimming is needed, the 3-bit LSBs should be kept as '111' while the 8-bit MSBs are programmed. If 11-bit dimming ratio is needed, the 3-bit LSBs should be programmed first, then the 8-bit MSBs are programmed. Only programming the 3-bit LSBs doesn't change the current ratio until the 8-bit MSBs are programmed.

April 2019 - Revision 04a Page 12 Company Confidential

In linear mapping 8-bit dimming mode, the LED current per channel can be calculated as:

$$I_{LED\_BL} = I_{LED\_FS} \times D_{PWM} \times \frac{Code + 1}{256} \qquad (Code = 0 \sim 255)$$

where I<sub>LED\_FS</sub> is the backlight full-scale LED current, D<sub>PWM</sub> is the input PWM duty cycle if PWM dimming is enabled, otherwise D<sub>PWM</sub>=1.

In linear mapping 11-bit dimming mode, the LED current per channel can be calculated as:

$$I_{LED\_BL} = I_{LED\_FS} \times D_{PWM} \times \frac{Code + 1}{2048} \qquad (Code = 1 \sim 2047)$$

For linear mapping 11-bit dimming's Code 0, current sink and boost converter will be disabled, LED will be turned off.

In exponential mapping 8-bit dimming mode, the LED current per channel can be calculated as:

$$I_{LED\_BL} = I_{LED\_FS} \times D_{PWM} \times \frac{1.002931237^{Code \times 8+7}}{400} \qquad (Code = 0 \sim 255)$$

In exponential mapping 11-bit dimming mode, the LED current per channel can be calculated as:

$$I_{LED\_BL} = I_{LED\_FS} \times D_{PWM} \times \frac{1.002931237^{Code}}{400}$$

(Code = 1 ~ 2047)

For exponential mapping 11-bit dimming's Code 0, current sink and boost converter will be disabled, LED will be turned off.

#### Flash LED Current

The flash LED current per channel is programmed by Flash Setting Register 0x09 Bits[3:0] (see Table 13), the equation is:

$$I_{LED\_FLASH} = \left(1 + \frac{Code + 1}{16}\right) \times 29.8mA \qquad (Code = 0 \sim 15)$$

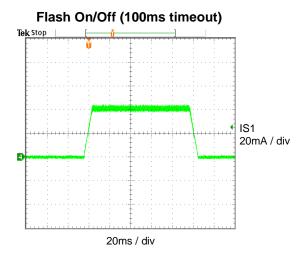

where Code is Flash Setting Register 0x09 Bits[3:0]'s setting. So the flash current can be programmed from 31.66mA to 59.6mA, with 59.6mA as the default setting. Flash mode current is not related to the input PWM duty cycle.

#### **Flash Timeout**

The flash timeout is programmed by Flash Setting Register 0x09 Bits[7:4] (see Table 13). It ranges from 100ms to 1.5sec with 100ms/step, 500ms is the default. If the switching frequency shift up by 20% is selected, the flash timeout will be decreased by 20%.

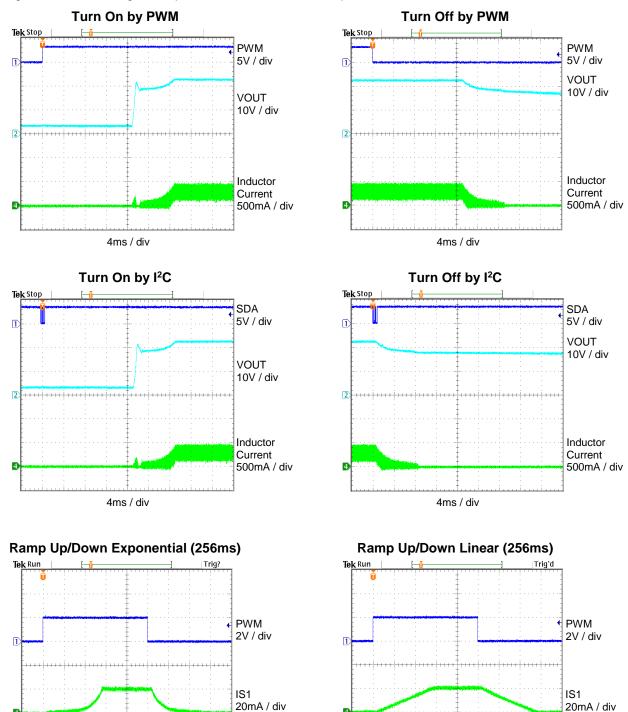

#### **Turn On/Off Ramp**

When backlight mode or flash mode is enabled from standby mode or disabled to standby mode, the LED current waveform's turn on/off time is controlled by Turn On/Off Ramp Register 0x07 Bits[7:4] and Bits[3:0] respectively (see Table 11). The 16 options range from 512µs to 16384ms, with 8ms as default. The shape of the turn on/off ramp in backlight mode can also be programmed as exponential or linear through the Control Register 0x03 Bit[2], with exponential as default. Flash mode's turn on/off ramp shape is always linear. If the switching frequency shift up by 20% is selected, all ramp times will be decreased by 20%.

#### I<sup>2</sup>C Dimming Transition Ramp

After the turn on ramp is finished, if the LED current is changed from one value to the other by  $I^2C$  dimming Register 0x04 and Register 0x05, the transition ramp time can be programmed by Transition Ramp Register 0x08 Bits[3:0] (see Table 12). For Code 0001~1111, there are 15 programmable options (128ms ~ 1024ms) of the ramp time, it is independent of the  $I^2C$  dimming code change and will keep the same no matter how big the

April 2019 - Revision 04a Page 13 Company Confidential

dimming code change is. For Code 0000, the slope of the ramp is fixed as 1us/step, so the final transition ramp time is dependent on the 11-bit I<sup>2</sup>C dimming code change. When the system switches between backlight mode and flash mode, the LED current transition ramp will always choose Code 0000 to minimize the transition time. If the switching frequency shift up by 20% is selected, all transition times will be decreased by 20%.

#### **PWM Dimming Transition Ramp**

After the turn on ramp is finished, if the LED current is changed from one value to the other by PWM dimming duty cycle, the transition ramp time can be programmed by Transition Ramp Register 0x08 Bits[6:4] (see Table 12). For this transition ramp, its slope is fixed, so the final transition ramp time is dependent on the change of the PWM duty cycle. If the switching frequency shift up by 20% is selected, all transition times will be decreased by 20%.

#### **Channel Enable/Disable**

To disable any channel, there are two options.

- Connect the associated sink pin to GND. During the startup, the IC will automatically detect and disable the corresponding channel.

- Program PWM Register 0x06 Bits[1:0] (See Table 10) to enable/disable the channel(s), with enable as

default.

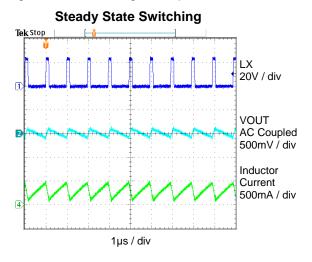

#### **Switching Frequency**

The step-up converter's switching frequency can be programmed to 1MHz or 500kHz by Control Register 0x03 Bit[6] (See Table 7), with 1MHz as default. The adjustment of the switching frequency can optimize the efficiency under different load current conditions. The frequency can also be programmed to shift up by 20% using the Control Register 0x03 Bit[7], with no shift as default. The frequency shift function is to prevent noise interference if the selected switching frequency is within the sensitive frequency range of the system.

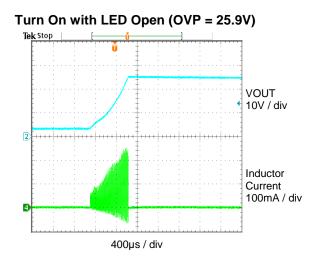

#### Over Voltage Protection (OVP)

The output voltage of the step-up converter is protected by OVP, its threshold can be programmed by the Control Register 0x03 Bit[5] (See Table 7) as 32V or 25.9V, with 32V as default.

#### **Inductor Current Limit Protection**

The step-up converter is protected by cycle-by-cycle inductor current limit protection, its threshold can be programmed by the Control Register 0x03 Bit[3] (See Table 7) as 2.6A or 1.8A, with 2.6A as default.

#### **Software Reset**

All the I<sup>2</sup>C registers can be reset to their default settings by writing '1' to the Software Reset Register 0x01 Bit[0] (see Table 5), this bit will be reset to '0' automatically after the software reset.

#### **LED Fault Protection**

Each current sink is protected against LED short or open conditions.

If LED short circuit condition arises, the current sink continues to regulate until the sink node voltage goes above V<sub>SOV</sub> (12V) for more than 6µs, then the Current Sink Fault Protection is triggered, the boost converter will be stopped to prevent VOUT from rising up, and current sink will be kept on to discharge VOUT.

In case of an LED failing open, the current sink voltage of the failed string will go close to ground and dominate the boost converter control loop. As a result, the output voltage will increase until it reaches the overvoltage threshold. Once the overvoltage incident is triggered, the boost converter will be turned off, and all the other healthy channels will be on to discharge VOUT. During the rise of VOUT, if the healthy channels' sink voltages reach  $V_{SOV}$  (12V) for  $6\mu$ s before VOUT reaches its overvoltage threshold, this will trigger LED short protection, not LED open protection.

After LED open or short protection, user needs to restart the IC by toggling HWEN or sending software reset command or resetting backlight/flash mode.

#### **UVLO**

Under voltage lock-out (UVLO) featured is included to monitor the input voltage VIN. Once VIN drops below UVLO falling threshold, the current sinks are disabled and the boost converter stops switching. After VIN increases above UVLO rising threshold, the boost converter and the current sinks will resume to their previous setting.

April 2019 - Revision 04a Page 14 Company Confidential

#### Thermal Shutdown

Thermal shutdown feature is included to monitor the IC's junction temperature. If it reaches 150°C, the current sinks are disabled and the boost converter stops switching. Once it drops 15°C to approximately 135°C, the boost converter and the current sinks will resume to their previous setting.

#### **Status Report**

Various status conditions can be reported through I<sup>2</sup>C interface by the read-only Status Register 0x0A (See Table 14), including channel fault (LED open or short), flash timeout, OVP, UVLO, OCP (inductor current limit) and thermal shutdown. Channel fault, UVLO and thermal shutdown are real-time results when backlight/flash mode is enabled and it can be reset by toggling backlight/flash mode. The remaining faults are latched results and can be reset by reading back Status Register 0x0A through I<sup>2</sup>C interface or toggling backlight/flash mode. All the status bits can also be reset by VIN power on reset, software reset or toggling HWEN.

## **Application Information**

#### I<sup>2</sup>C Serial Data Bus

KTD3134 supports the I<sup>2</sup>C bus protocol. A device that sends data onto the bus is defined as a transmitter and a device receiving data as a receiver. The device that controls the bus is called a master, whereas the devices controlled by the master are known as slaves. A master device must generate the serial clock (SCL), control bus access and generate START and STOP conditions to control the bus. KTD3134 operates as a slave on the I<sup>2</sup>C bus. Within the bus specifications a standard mode (100kHz maximum clock rate) and a fast mode (400kHz maximum clock rate) are defined. KTD3134 works in both modes. Connections to the bus are made through the open-drain I/O lines SDA and SCL.

The following bus protocol has been defined in Figure 4:

- Data transfer may be initiated only when the bus is not busy.

- During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is high are interpreted as control signals.

Accordingly, the following bus conditions have been defined:

#### **Bus Not Busy**

Both data and clock lines remain HIGH.

#### Start Data Transfer

A change in the state of the data line, from HIGH to LOW, while the clock is HIGH, defines a START condition.

#### Stop Data Transfer

A change in the state of the data line, from LOW to HIGH, while the clock line is HIGH, defines the STOP condition.

#### Data Valid

The state of the data line represents valid data when, after a START condition, the data line is stable for the duration of the HIGH period of the clock signal. The data on the line must be changed during the LOW period of the clock signal. There is one clock pulse per bit of data.

Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of data bytes transferred between START and STOP conditions are not limited, and are determined by the master device. The information is transferred byte-wise and each receiver acknowledges with a ninth bit.

#### **Acknowledge**

Each receiving device, when addressed, is obliged to generate an acknowledge after the reception of each byte. The master device must generate an extra clock pulse that is associated with this acknowledge bit.

A device that acknowledges must pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge-related clock pulse. Setup and hold times must also be taken into account.

April 2019 - Revision 04a Page 15 Company Confidential

Figure 4. Data Transfer on I<sup>2</sup>C Serial Bus

KTD3134 7-bit slave device address is 0110110 binary (0x36h).

There are two kinds of I<sup>2</sup>C data transfer cycles: write cycle and read cycle.

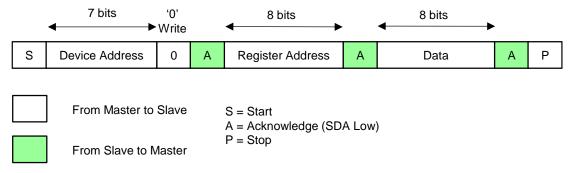

#### I<sup>2</sup>C Write Cycle

For I<sup>2</sup>C write cycle, data is transferred from a master to a slave. The first byte transmitted is the 7-bit slave address plus one bit of '0' for write. Next follows a number of data bytes. The slave returns an acknowledge bit after each received byte. Data is transferred with the most significant bit (MSB) first. Figure 5 shows the sequence of the I<sup>2</sup>C write cycle.

Figure 5. I<sup>2</sup>C Write Cycle

#### I<sup>2</sup>C Write Cycle Steps:

- Master generates start condition.

- Master sends 7-bit slave address (0110110 for KTD3134) and 1-bit data direction '0' for write.

- Slave sends acknowledge if the slave address is matched.

- · Master sends 8-bit register address.

- · Slave sends acknowledge.

- · Master sends 8-bit data for that addressed register.

- Slave sends acknowledge.

- If master sends more data bytes, the register address will be incremented by one after each acknowledge.

- Master generate stop condition to finish the write cycle.

April 2019 - Revision 04a Page 16 Company Confidential

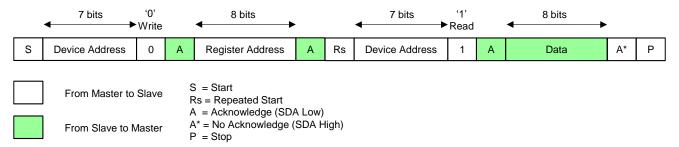

#### I<sup>2</sup>C Read Cycle

For I<sup>2</sup>C read cycle, data is transferred from a slave to a master. But to start the read cycle, master needs to write the register address first to define which register data to read. Figure 6 shows the steps of the I<sup>2</sup>C read cycle.

Figure 6. I<sup>2</sup>C Read Cycle

#### I<sup>2</sup>C Read Cycle Steps:

- · Master generates start condition.

- Master sends 7-bit slave address (0110110 for KTD3134) and 1-bit data direction '0' for write.

- Slave sends acknowledge if the slave address is matched.

- Master sends 8-bit register address.

- Slave sends acknowledge.

- Master generates repeated start condition.

- Master sends 7-bit slave address (0110110 for KTD3134) and 1-bit data direction '1' for read.

- Slave sends acknowledge if the slave address is matched.

- Slave sends the data byte of that addressed register.

- If master sends acknowledge, the register address will be incremented by one after each acknowledge and the slave will continue to send the data for the updated addressed register.

- If master sends no acknowledge, the slave will stop sending the data.

- Master generate stop condition to finish the read cycle.

#### I<sup>2</sup>C Register Map

Table 3 summarizes KTD3134's 11 I<sup>2</sup>C registers, their read/write settings and default values. They can be reset to default values by VIN power on reset, toggling HWEN or I<sup>2</sup>C software reset.

Table 3. I<sup>2</sup>C Register Map

| Register Name                  | Address (Hex) | R/W | Default Value |

|--------------------------------|---------------|-----|---------------|

| Device ID Register             | 0x00          | R   | 18            |

| SW Reset Register              | 0x01          | R/W | 00            |

| Mode Register                  | 0x02          | R/W | 98            |

| Control Register               | 0x03          | R/W | 68            |

| LED Current Ratio LSB Register | 0x04          | R/W | 07            |

| LED Current Ratio MSB Register | 0x05          | R/W | FF            |

| PWM Register                   | 0x06          | R/W | 1F            |

| Turning On/Off Ramp Register   | 0x07          | R/W | 44            |

| Transition Ramp Register       | 0x08          | R/W | 00            |

| Flash Setting Register         | 0x09          | R/W | 5F            |

| Status Register                | 0x0A          | R   | 00            |

#### Table 4. Device ID Register (0x00)

| Bits[7:5] | Bits[5:3]<br>Device ID | Bits[2:0] |

|-----------|------------------------|-----------|

| Reserved  | 011                    | Reserved  |

#### Table 5. SW Reset Register (0x01)

| Bits[7:1] | Bit[0]<br>Software Reset             |

|-----------|--------------------------------------|

| Reserved  | 0: Don't reset (Default)<br>1: Reset |

Note: Writing software reset bit to '1' will reset all I<sup>2</sup>C registers to their default values, then this bit will be internally reset back to '0'.

#### Table 6. Mode Register (0x02)

| Bits[7:3] Backlight Full-scale LED Current I <sub>LED_FS</sub>                                                                 | Bit[2]   | Bit[1]<br>Flash Mode              | Bit[0]<br>Backlight Mode          |

|--------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------------------|-----------------------------------|

| I <sub>LED_FS</sub> = 5mA + Code x 0.8mA<br>11111 : 29.8mA<br><br>10011 : 20.2mA (Default)<br><br>00001 : 5.8mA<br>00000 : 5mA | Reserved | 0: Disable (Default)<br>1: Enable | 0: Disable (Default)<br>1: Enable |

Note: Flash Mode bit has higher priority over Backlight Mode bit. If both bits are high, flash mode is selected. After flash mode timeout, Flash Mode bit is reset to '0' automatically.

#### Table 7. Control Register (0x03)

| Bit[7]<br>Switching<br>Frequency Shift<br>Up | Bit[6]<br>Switching<br>Frequency | Bit[5]<br>OVP<br>Control | Bit[4]          | Bit[3]<br>Inductor<br>Current<br>Limit | Bit[2]<br>Backlight<br>Turn On/Off<br>Ramp Shape | Bit[1]<br>Backlight<br>Current<br>Mapping | Bit[0]   |

|----------------------------------------------|----------------------------------|--------------------------|-----------------|----------------------------------------|--------------------------------------------------|-------------------------------------------|----------|

| 0: No Shift                                  | 0: 500kHz                        | 0: 25.9V                 | Reserved        | 0: 1.8A                                | 0: Exponential                                   | 0 : Exponential                           | Reserved |

| (Default)                                    | 1: 1000kHz                       | 1: 32V                   | Must be written | 1: 2.6A                                | (Default)                                        | (Default)                                 |          |

| 1: Shift Up by 20%                           | (Default)                        | (Default)                | with "0"        | (Default)                              | 1: Linear                                        | 1 : Linear                                |          |

Note: When Backlight Current Mapping setting is changed, the LED current change will not take effect until Register 0x05 is programmed.

#### Table 8. Brightness Register LSB (0x04)

| Bits[7:3] | Bits[2:0]<br>LED Current Ratio LSBs (3 bits)                |  |  |

|-----------|-------------------------------------------------------------|--|--|

| Reserved  | Lower 3 bits of the 11-bit LED current ratio (Default: 111) |  |  |

#### Table 9. Brightness Register MSB (0x05)

| Bits[7:0]<br>LED Current Ratio MSBs (8 bits)                      |  |  |  |  |

|-------------------------------------------------------------------|--|--|--|--|

| Higher 8 bits of the 11-bit LED current ratio (Default: 11111111) |  |  |  |  |

#### Note:

- 1. If only using 8-bit current ratio, keep the 3-bit LSBs as '111' and only program the 8-bit MSBs.

- If using 11-bit current ratio, the 3-bit LSBs should be programmed first, then the 8-bit MSBs can be programmed to take effect. Even if only the 3-bit LSBs need to be changed, the 8-bit MSB should always be programmed next to make the 3-bit LSBs change taking effect.

- 3. For 11-bit program code 11'b00000000000, both boost converter and current sinks are turned off.

April 2019 - Revision 04a Page 18 Company Confidential

### Table 10. PWM Register (0x06)

| Bit[7]                               | Bit[6]                                       | Bits[5:3]                                                                                                                       | Bit[2]   | Bit[1]                            | Bit[0]                            |

|--------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------------------|-----------------------------------|

| PWM Enable                           | PWM Active                                   | PWM Hysteresis                                                                                                                  |          | CH2 Enable                        | CH1 Enable                        |

| 0: Enable<br>(Default)<br>1: Disable | 0: High Active<br>(Default)<br>1: Low Active | 000: 0 LSB<br>001: 2 LSBs<br>010: 4 LSBs<br>011: 6 LSBs (Default)<br>100: 8 LSB<br>101: 10 LSBs<br>110: 12 LSBs<br>111: 14 LSBs | Reserved | 0: Disable<br>1: Enable (Default) | 0: Disable<br>1: Enable (Default) |

Table 11. Turn On/Off Ramp Register (0x07)

| Bits[7:4]<br>Turn On Ramp Time | Bits[3:0] Turn Off Ramp Time |

|--------------------------------|------------------------------|

| 0000: 512μs                    | 0000: 512μs                  |

| 0001: 1ms                      | 0001: 1ms                    |

| 0010: 2ms                      | 0010: 2ms                    |

| 0011: 4ms                      | 0011: 4ms                    |

| 0100: 8ms (Default)            | 0100: 8ms (Default)          |

| 0101: 16ms                     | 0101: 16ms                   |

| 0110: 32ms                     | 0110: 32ms                   |

| 0111: 64ms                     | 0111: 64ms                   |

| 1000: 128ms                    | 1000: 128ms                  |

| 1001: 256ms                    | 1001: 256ms                  |

| 1010: 512ms                    | 1010: 512ms                  |

| 1011: 1024ms                   | 1011: 1024ms                 |

| 1100: 2048ms                   | 1100: 2048ms                 |

| 1101: 4096ms                   | 1101: 4096ms                 |

| 1110: 8192ms                   | 1110: 8192ms                 |

| 1111: 16384ms                  | 1111: 16384ms                |

Note: If the switching frequency shift up by 20% is selected, all the ramp times will be decreased by 20%.

April 2019 - Revision 04a Page 19 Company Confidential

Table 12. Transition Ramp Register (0x08)

| Bit[7]   | Bits[6:4] PWM Dimming Transition Ramp Time                                                                            | Bits[3:0] I <sup>2</sup> C Dimming Transition Ramp Time                                                                                                                                                                       |  |  |

|----------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Reserved | 000 : 2ms (Default)<br>001 : 4ms<br>010 : 8ms<br>011 : 16ms<br>100 : 32ms<br>101 : 64ms<br>110 : 128ms<br>111 : 256ms | 0000 : 1μs/step (Default) 0001 : 128ms 0010 : 192ms 0011 : 256ms 0100 : 320ms 0101 : 384ms 0110 : 448ms 0111 : 512ms 1000 : 576ms 1001 : 640ms 1010 : 704ms 1011 : 768ms 1100 : 832ms 1101 : 896ms 1110 : 960ms 1111 : 1024ms |  |  |

#### Note:

- 1. If the switching frequency shift up by 20% is selected, all the transition times will be decreased by 20%.

- 2. The PWM Dimming Transition Ramp Time in the table is defined as the time to change between minimum PWM duty cycle and the maximum PWM duty cycle. The final transition time is the multiplication of the time in the table and the change of the PWM duty cycle.

- 3. For I<sup>2</sup>C Dimming Transition Ramp Time in the table, all the ramp times are fixed when current ramps from one level to the other except "0000" setting. For "0000" setting, the ramp slope is 1us/step, the final ramp time is proportional to the 11-bit current steps.

Table 13. Flash Setting Register (0x09)

| Bits[7:4]                                                                                                                                                                                                                    | Bits[3:0]                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Flash Timeout                                                                                                                                                                                                                | Flash Current                                                                                                                                                                                                                                                                                                   |

| 0000 : No Flash Timeout 0001 : 100ms 0010 : 200ms 0011 : 300ms 0100 : 400ms 0101 : 500ms (Default) 0110 : 600ms 0111 : 700ms 1000 : 800ms 1001 : 900ms 1010 : 1000ms 1011 : 1100ms 1101 : 1300ms 1101 : 1300ms 1111 : 1500ms | I <sub>FLASH</sub> = (1 + (Code+1) / 16) x 29.8mA<br>0000: 31.66mA<br>0001: 33.53mA<br>0010: 35.39mA<br>0011: 37.25mA<br>0100: 39.11mA<br>0101: 40.98mA<br>0110: 42.84mA<br>0111: 44.7mA<br>1000: 46.56mA<br>1001: 48.43mA<br>1010: 50.29mA<br>1011: 52.15mA<br>1100: 54.01mA<br>1101: 55.88mA<br>1110: 57.74mA |

Note: If the switching frequency shift up by 20% is selected, the flash timeout will be decreased by 20%.

Table 14. Status Register (0x0A)

| Bit[7]   | Bit[6]                                 | Bit[5]                                 | Bit[4]                                        | Bit[3]                           | Bit[2]                            | Bit[1]                           | Bit[0]                                           |

|----------|----------------------------------------|----------------------------------------|-----------------------------------------------|----------------------------------|-----------------------------------|----------------------------------|--------------------------------------------------|

| Reserved | 0: Normal<br>(Default)<br>1: CH2 Fault | 0: Normal<br>(Default)<br>1: CH1 Fault | 0: Normal<br>(Default)<br>1: Flash<br>Timeout | 0: Normal<br>(Default)<br>1: OVP | 0: Normal<br>(Default)<br>1: UVLO | 0: Normal<br>(Default)<br>1: OCP | 0: Normal<br>(Default)<br>1: Thermal<br>Shutdown |

#### Note:

- CH1/2 fault, UVLO and thermal shutdown are real-time results when backlight/flash mode is enabled and can be reset by toggling backlight/flash mode.

- Flash timeout, OVP and OCP are latched results and can be reset by reading back Status Register 0x0A through I<sup>2</sup>C or toggling backlight/flash mode.

- 3. All the status bits can be reset by VIN power on reset, software reset or toggling HWEN.

#### **Capacitor Selection**

Small size ceramic capacitors with low ESR are ideal for all applications. A  $10\mu\text{F}$  input capacitor and a  $1\mu\text{F}\sim2.2$   $\mu\text{F}$  output capacitor are suggested. The voltage rating of these capacitors should exceed the maximum possible voltage at the corresponding pins, and these capacitors should be as close as possible to the IC. Table 15 shows the recommended capacitor vendors.

**Table 15. Recommended Capacitor Vendors**

| Manufacturer | Website         |  |

|--------------|-----------------|--|

| Murata       | www.murata.com  |  |

| AVX          | www.avx.com     |  |

| Taiyo Yuden  | www.t-yuden.com |  |

#### **Inductor Selection**

An inductor of  $4.7\mu H$  to  $10\mu H$  with low DCR can be selected for the boost converter. To decide the current rating of the inductor required for the application, the following equation can be used to estimate the peak inductor current IPEAK in continuous conduction mode (CCM):

$$I_{PEAK} = \frac{V_{OUT(MAX)} \times I_{OUT(MAX)}}{V_{IN(MIN)} \times \eta} + \frac{V_{IN(MIN)}}{2L \times F_{SW}} \times \left(1 - \frac{V_{IN(MIN)}}{V_{OUT(MAX)}}\right)$$

where  $V_{OUT(MAX)}$  is the maximum output voltage,  $V_{IN(MIN)}$  is the minimum input voltage,  $I_{OUT(MAX)}$  is the maximum output current,  $F_{SW}$  is the boost converter's switching frequency, L is the inductor value,  $\eta$  is the boost converter's efficiency under that condition. Table 16 shows recommended inductors under different application conditions.

**Table 16. Recommended Inductors**

| Application              | Inductor Part<br>Number | Value<br>(µH) | DCR<br>(mΩ) | Saturation<br>Current (A) | Dimensions (mm) | Manufacturer |

|--------------------------|-------------------------|---------------|-------------|---------------------------|-----------------|--------------|

| 2P7S<br>(Max. 20mA/Ch)   | LQH3NPN100MJR           | 10            | 240 typ     | 0.810                     | 3.0 x 3.0 x 1.1 | Murata       |

| 2P7S<br>(Max. 59.6mA/Ch) | FDSD0412-H-4R7M         | 4.7           | 161 max     | 1.9                       | 4.2 x 4.2 x 1.2 | Murata       |

| 2P7S<br>(Max. 59.6mA/Ch) | SRP5030T-100M           | 10            | 128 max     | 2.75                      | 5.7 x 5.2 x 2.8 | Bourns       |

#### **Schottky Diode Selection**

Using a schottky diode is recommended because of its low forward voltage drop and fast reverse recovery time. The average current rating of the schottky diode should exceed the maximum output current, and its peak current rating should exceed the peak inductor current. Its voltage rating should also exceed the OVP setting. Table 17 shows the recommended schottky diode.

Table 17. Recommended Schottky Diode

| Application | Schottky Diode<br>Part Number | Forward<br>Voltage (V) | Forward<br>Current (A) | Reverse<br>Voltage (V) | Manufacturer |

|-------------|-------------------------------|------------------------|------------------------|------------------------|--------------|

| All         | PMEG4010B                     | 0.54                   | 1                      | 40                     | NXP          |

April 2019 - Revision 04a Page 21 Company Confidential

#### **Recommended PCB Layout**

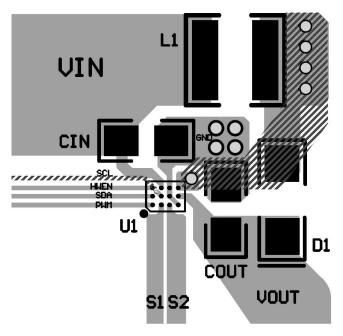

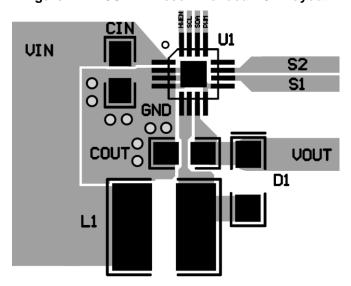

PCB layout is very important for high frequency switching regulators in order to keep the loop stable and minimize noise. The input capacitor (C<sub>IN</sub>) should be very close to the IC's VIN pin and PGND pin in order to get the best decoupling. The path between the inductor, LX pin, schottky diode and the output capacitor (C<sub>OUT</sub>) should be kept as short as possible to minimize noise and ringing. To reduce power loss, the trace through the inductor, LX pin, schottky diode and C<sub>OUT</sub> should be as short and wide as possible. Both input and output capacitors' GND terminals should be connected together on the PCB top layer and on the bottom layer GND plane. Figure 7 shows the WLCSP-12 recommended PCB layout and Figure 8 shows the TQFN-16 recommended PCB layout.

Figure 7. WLCSP-12 Recommended PCB Layout

Figure 8. TQFN-16 Recommended PCB Layout

April 2019 - Revision 04a Page 22 Company Confidential

# **Packaging Information**

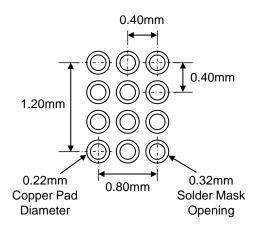

#### WLCSP34-12 (1.190mm x 1.640mm x 0.62mm)

#### **Recommended Footprint**

#### (NSMD Pad Type)

<sup>\*</sup> Dimensions are in millimeters.

April 2019 - Revision 04a Page 23 Company Confidential

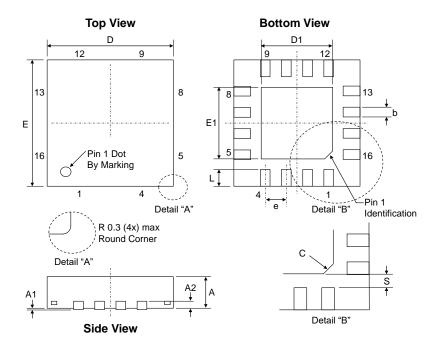

### TQFN33-16 (3.00mm x 3.00mm x 0.75mm)

| Dimension | mm    |         |       |  |  |  |

|-----------|-------|---------|-------|--|--|--|

| Dimension | Min.  | Тур.    | Max.  |  |  |  |

| А         | 0.65  | 0.75    | 0.85  |  |  |  |

| A1        | 0.000 | 0.025   | 0.050 |  |  |  |

| A2        | 0.154 | 0.203   | 0.280 |  |  |  |

| b         | 0.18  | 0.23    | 0.30  |  |  |  |

| С         |       | 0.3REF  |       |  |  |  |

| D         | 2.95  | 3.00    | 3.05  |  |  |  |

| D1        |       | 1.7REF  |       |  |  |  |

| E         | 2.95  | 3.00    | 3.05  |  |  |  |

| E1        |       | 1.7REF  |       |  |  |  |

| е         | 0.45  | 0.50    | 0.55  |  |  |  |

| L         | 0.30  | 0.40    | 0.50  |  |  |  |

| S         |       | 0.25REF |       |  |  |  |

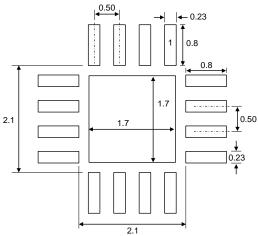

### **Recommended Footprint**

<sup>\*</sup> Dimensions are in millimeters.

Kinetic Technologies cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Kinetic Technologies product. No intellectual property or circuit patent licenses are implied. Kinetic Technologies reserves the right to change the circuitry and specifications without notice at any time.

April 2019 - Revision 04a Page 24 Company Confidential