**Application Note AN018**

# Thermal Characterization & QFN Layout Guide:

for the AS11xx Product Family

Revision 1.1, November 2017

# CONTENTS

| introduction                                   | 3  |

|------------------------------------------------|----|

| QFN Heat-Sink                                  | 3  |

| As11xx Family PD Controllers                   |    |

| Typical Power Dissipation in the AS11xx Family | 4  |

| Silicon Junction Temperature                   |    |

| Guidelines for PCB Layout                      | 6  |

| PCB Lavout                                     | 6  |

| Solder Mask Design                             | 8  |

| Preparing Thermal Vias for Solder Reflow       | 9  |

| Stencil Design                                 | 9  |

| Solder Process                                 |    |

| Rework                                         | 10 |

| Contact Information                            |    |

| Important Notices                              | 12 |

| Legal Notice                                   |    |

|                                                |    |

# INTRODUCTION

The Kinetic AS11xx product family of PoE PD1 controllers consist of the AS1113, AS1114 and AS1138. All devices are implemented in a 5mm square Quad Flat-pack, No-lead (QFN) package. In the QFN, the silicon die is mounted on a copper paddle, which is part of a stamped or etched lead frame. The die and lead frame are encapsulated in plastic with conventional transfer molding methods. Rather than having leads extending from the sides, the leads are brought out as exposed pads on the bottom surface of the package. The copper paddle is also exposed, providing both a ground connection and a direct thermal path between the die and the outside surface of the package. This construction provides for a small device footprint and exceptional thermal performance.

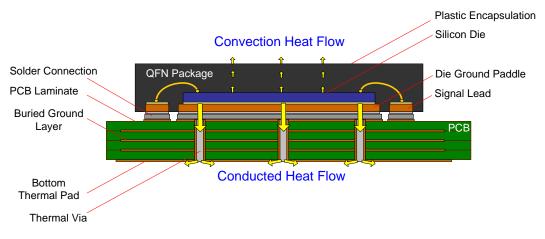

#### QFN Heat-Sink

As depicted in Figure 1, most of the heat generated by the PD device is removed by conduction through the bottom surface of the package. The heat sink is essentially built into the system Printed Circuit Board (PCB). To effectively remove the heat, the PCB must provide underlying thermal pads. The PCB top layer design should include a ground paddle with thermal vias. The vias should be connected to internal ground layers and a bottom-side thermal pad. Thermal energy form the package will be drawn down the vias and away from the package. The buried ground planes and bottom thermal pad should extend beyond the dimensions of the QFN package. This will help distribute the heat energy and spread it away from the QFN package.

Figure 1: Cross Section of QFN package mounted on a printed circuit board

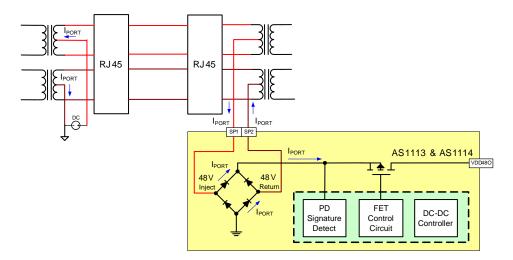

## AS11xx Family PD Controllers

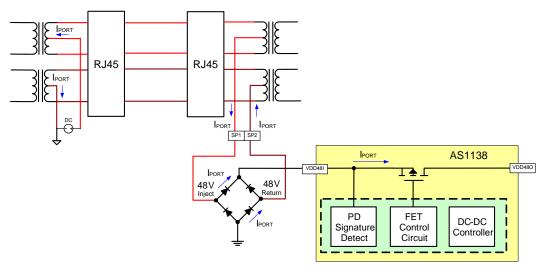

Kinetic provides the industry's smallest footprint solution for the PoE PD function. This small footprint has been accomplished by also integrating bridge diodes, protection circuitry and a DC-DC controller. Figure 2 depicts block diagrams for the Kinetic PD controllers. Both the AS1113 and AS1114 feature integrated bridge rectification while the higher power AS1138 solution uses external diodes.

When PoE power is applied, current flows through two of the diodes within the bridge rectifier. As depicted in Figures 2 and 3, each diode passes the full current delivered to the PD (IPORT). For PoE Type 1 applications, the diode current can be as large as 350mA while for Type 2 PDs, the diode current can be 720mA. Approximately 60% of the heat dissipated in PD Controller stems from the bridge rectification diodes. Another 25% comes from the internal FET switch. The remaining logic and control circuitry consumes only 8mA and contribute less than 20% to the chip's overall heat dissipation.

<sup>&</sup>lt;sup>1</sup> Power Over Ethernet (PoE) Powered Device (PD)

Figure 2: Block Diagrams for AS1113 and AS1114 PD Controller with Internal Diode Bridge

Figure 3: Block Diagrams for AS1138 PD Controller with External Diode Bridge

## Typical Power Dissipation in the AS11xx Family

Each of the Kinetic PD controllers has been designed for different power classes. The AS1113 and AS1114 were developed to address applications per the 802.3at specification for Type 1 PDs. This device offers the industry's smallest application footprint. However, with higher integration comes more heat generation. In comparison, the AS1138 was developed for 30W applications. This device was designed in accordance with the 802.3at specification for Type 1 and Type 2 PDs and will draw over 720mA under full load conditions. The diode bridge is omitted from the AS1138, specifically to manage the heat dissipation within the QFN package.

To calculate the power dissipation, we have the following relation:

$P_{\text{DISS}} = 2 \text{ }^{*}\text{V}_{\text{F}} \text{ }^{*}\text{ }I_{\text{PORT}} \text{ } \text{ } \text{ }I_{\text{PORT}}^{2} \text{ }^{*}\text{ }R_{\text{DSON}} \text{ } \text{ }\text{ }\text{ }\text{ }V_{\text{IN}} \text{ }\text{ }\text{ }\text{ }8\text{mA}$

Δ

Power dissipated in the bridge diodes follows a  $V_F * I$  relationship, where  $V_F$  is the forward voltage drop of the bridge diodes. The power dissipated in the internal FET switch is based on an I<sup>2</sup>R relationship while dissipation in remaining circuitry can be

calculated by multiplying the bias current (8mA) by the operating voltage (48V). Table 1 summarizes the calculated power dissipation for each of the Kinetic PoE PD Controllers.

| PD Device | I <sub>PORT</sub><br>Operating<br>Current | R <sub>DS_ON</sub><br>Maximum<br>FET<br>Switch<br>Resistance | V <sub>F</sub><br>Bridge<br>Diode<br>Forward<br>Voltage | P <sub>DIODE</sub><br>Dissipation<br>in bridge<br>diodes | P <sub>FET</sub><br>Dissipation in<br>FET Switch | P <sub>Control</sub><br>Dissipation<br>in PD and<br>DC-DC<br>Controller | P <sub>TOTAL</sub><br>Total Power<br>Dissipation<br>within the PD<br>Controller |

|-----------|-------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| AS1113/14 | 350mA                                     | 2.0Ω                                                         | 0.9V                                                    | 0.63W                                                    | 0.24W                                            | 0.38W                                                                   | 1.25W                                                                           |

| AS1138    | 720mA                                     | 1.5Ω                                                         | 0.9V                                                    | 1.30W (external)                                         | 0.78W                                            | 0.38W                                                                   | 1.16W <sup>1</sup>                                                              |

| Table 1. | Key parameters a | nd power budget for th | e Kinetic PD Controllers |

|----------|------------------|------------------------|--------------------------|

|----------|------------------|------------------------|--------------------------|

1. bridge diodes are external

Thermal measurements on the Kinetic reference designs show that the AS1113, AS1114 and AS1138 case temperature will generally reside around 40°C under no load conditions and rise to about 52°C under full load.

#### Silicon Junction Temperature

If mounted properly, the QFN package and PCB board will provide enough heat dissipation to keep the silicon junction temperature under 145°C<sup>2</sup>. Reliability data for the silicon process indicates that operation under this temperature limit will result in an overall failure rate of less than 21 FIT (1 failure / billion devices).

The power dissipation numbers published in the Kinetic datasheets have been guard-banded to represent worst case corner conditions. Table 2 identifies published power dissipation and the worst case junction temperatures. If mounted properly, the QFN package will exhibit a junction-to-ambient thermal resistance,  $\theta_{JA}$ , of 31°C/W. As indicated in the table, the QFN package provides plenty of heat dissipation to maintain the silicon junction at reliable levels.

Also, it should be noted that the Kinetic PD Controller provides protection against thermal breakdown. An internal temperature monitor inside the Kinetic PD will begin to limit the current flowing through the internal FET, when the junction temperature reaches 145°C. If the device continues to heat-up, the FET will shut-off completely when the junction temperature reaches 160°C.

| PD Device | <b>P</b> TOTAL<br>Worst Case Power<br>Dissipation within<br>the device | ΔT <sub>JA</sub><br>Junction to Ambient<br>Temperature<br>Differential at Max<br>Power | T <sub>J25°C</sub><br>Junction Temperature<br>at 25°C ambient | TJ70℃<br>Junction Temperature<br>at 70℃ ambient | T <sub>J85</sub> ℃<br>Junction<br>Temperature at<br>85℃ ambient |

|-----------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------|-----------------------------------------------------------------|

| AS1113/14 | 1.5W                                                                   | 46.5°C                                                                                 | 71.5°C                                                        | 117.5°C                                         | 131.5℃                                                          |

| AS1138    | 1.7W                                                                   | 52.7°C                                                                                 | 77.7°C                                                        | 122.7°C                                         | 137.7°C                                                         |

<sup>&</sup>lt;sup>2</sup> The silicon process used by Kinetic is capable of reliable operation up to junction temperatures of 160°C

#### **GUIDELINES FOR PCB LAYOUT**

The following design guideline provides detailed design instruction for laying-out the system PCB to accept the Kinetic PC Controller. When laying-out the system board, the design guide should be used in conjunction with the datasheet and reference design to assure good thermal dissipation. If there are any questions or concerns, please contact Kinetic applications team through your sales contact or support@kinet-ic.com

#### **PCB Layout**

As described earlier, the QFN package does not have solder balls. Electrical connection between the package and the system PCB is achieved by printing the solder paste on the system board and then reflowing the solder in a convection or infra-red (IR) oven. Reliable solder joints depend on both the PCB pad size and solder application process.

As described above, the heat sink for the QFN package is built into the system PCB. Good solder attachment is necessary for effective removal of heat generated by the PD. To achieve the desired electrical and thermal performance, the exposed thermal pad on the underside of the QFN package must be soldered to a corresponding thermal plane on the system PCB with a minimal number of voids. Care must be taken during assembly and reflow to minimize voids at the solder interface between the QFN ground paddle and PCB pad. Voids can occur due to out-gassing of solvents during the solder reflow and from solder wicking down into the thermal vias. If voids become too prominent, (>60% of the pad area), they will increase the thermal resistance of the solder interface and diminish the heat dissipation to ground pads on the system PCB. If there is a good solder interface, the thermal vias will be very effective in carrying heat away from the QFN package and distributing it to the ground planes and thermal pad on the backside of the PCB.

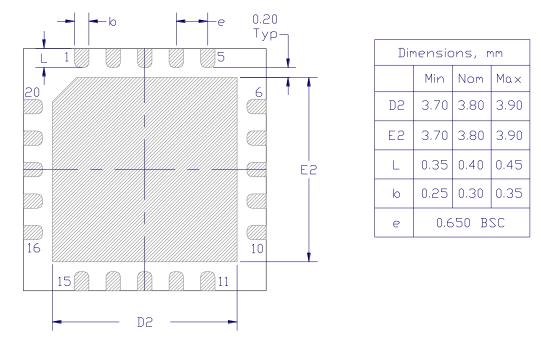

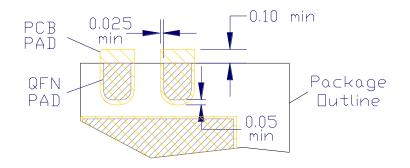

Figure 4 shows the dimensions for the 5mm QFN package<sup>3</sup>. When designing the landing pads on the system PCB, it is recommended than the PCB lead fingers be a minimum 0.10mm longer than the package land length. The Kinetic QFN package has a nominal lead length of 0.40mm. The lead pads should be designed to be at least 0.60mm long and positioned so that they also extended 0.05mm towards the center of the package. As shown in Figure 5, the pad width should be a minimum of 0.05mm (0.025mm per side) larger than the pad width on the QFN package. Electro-less nickel / immersion gold or electroplated nickel / gold finishes provide a good surface. Typically, 5µm of nickel and 0.05 to 0.10µm of gold are required to avoid brittle solder joints.

<sup>&</sup>lt;sup>3</sup> Based on the IPC-SM-782 is the industry standard for PCB land patterns.

Figure 4: QFN Pad Dimensions, (viewed through the package)

Figure 5: PCB Pad Dimensions

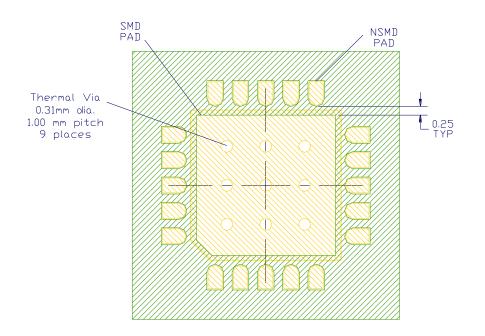

The number of thermal vias will determine how effectively heat is removed from the package. In the 5mm QFN package, 9 vias are practical on a 1mm pitch. A minimum via diameter of 0.31mm (0.012 inch) is recommended. Larger diameters, up to 0.61mm, may be used if necessary. In all cases, the barrel of the vias should be plated up to 1oz Cu. For the 0.31mm hole, this will effectively close the barrel to < 0.25mm.

The thermal pad of the QFN package also serves as the device electrical ground. The thermal vias should also connect to buried ground planes, within the PCB stack. On the back surface, the thermal vias should also connect to a ground pad. From the various ground pads, heat will spread through conduction and then dissipate through convection. In general, it is best to design the ground pads as large as possible to spread the head and improve the convection process. Temperature sensitive components should be place a minimum 0.100" (2.5mm too) from the thermal pad. On the top surface of the PCB, the case temperature will run about 10°C cooler than the bottom pad. Most SMT chip resistors are stable enough to be placed close to the PC Controller. However, consult the manufacture's data sheet prior to laying out the PCB.

#### Solder Mask Design

The pads printed on the PCB can either be Solder Mask Defined (SMD) or Non Solder Mask Defined (NSMD). For the peripheral input/output pads, NSMD recommended over SMD pads, since the copper etching process has tighter tolerance control than solder mask process. The solder mask aperture should be set-back 60 to 75µm from the copper pads. This means that the solder mask opening be designed to be 120 to 150µm larger than the pad size. This allows for solder mask registration tolerances, which are typically in the range of 50µm. Using NSMD pads also improves the reliability at the solder joint. When the solder paste reflows, it is allowed to wrap around the edges of the metal pads. Figure 6 depicts the solder mask. With the 0.65mm lead pitch, the solder mask provides approximately 0.60mm of separation, which is sufficient to prevent bridging between lead pads. The area of greater concern is between the thermal paddle and leads. Here, it is recommended that a SMD design be used. The edge of the solder mask should be set-in to assure that there is 0.25mm of solder mask between the exposed thermal paddle and the device leads.

Figure 6: PCB land pattern and solder mask

#### Preparing Thermal Vias for Solder Reflow

During the solder reflow process, solder will tend to "wick" down the via barrels, drawing solder away from the paddle and creating voids. There are a few options to prevent this wicking effect.

- One is to plug the vias using solder or a thermally stable epoxy. Plugging the vias will provide good control over the package stand-off height. Plugged holes will also remove the opportunity for air entrapment and the solder wicking. The drawback of plugging the holes is that it adds process steps to the production flow.

- A simpler solution is to "tent" the holes by covering them with solder mask on the bottom-side of the PCB. A Liquid Photo-Image mask (LPI) is recommended. When applied some of the mask material will partially fill the hole. During IR reflow, air will out-gas from the top of the vias and counteract the capillary forces that tend to draw the solder down into the barrel of the via. The designer has the option of either covering the entire thermal pad or may either simply covering the via holes with a circular skin, often referred to as "tenting". The tenting diameter should be 100µm larger than the via hole diameter. For instance, a 0.41mm pad should be used to cover a 0.31mm hole.

#### Stencil Design

The stencil design has much impact on the quality of the solder joints. Optimum solder joints should provide the QFN package a stand-off height of 50 to 70µm from the system PCB. After solder reflow, inspection should show a good fillet "foot" on the input/output pads. A joint with less height, that exhibits leads without the fillet foot, indicates insufficient solder. If there is not enough solder at the interface, the part will have limited mechanical integrity under shock and vibration. If inspection shows a stand-off between the QFN package and system PC of over 70µm, this indicated is that too much solder is applied to the joint. Another indication is solder bulging at the input/output pads, rather than a fillet foot. With too much solder, the devices are susceptible to shorts underneath the QFN package. The stencil design provides one means of controller the amount of solder applied at the interface. Often, some experimentation and visual inspection on a number of parts, is required to get the right settings.

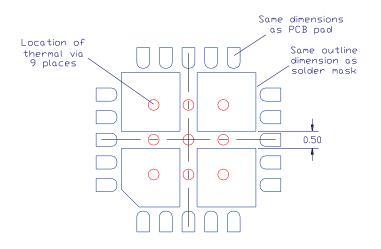

Solder paste consists of 40% metal alloys and 60% binders, solvents and flux. During the IR reflow process, these materials boil-out of the paste and evaporate. As described above, the thermal vias can also out-gas during the IR reflow operation. If not addressed, the out-gassing of materials can cause solder bridging and voids. A common technique is to provide lanes in the solder stencil, that provide a path for out-gassing solvents.

To effectively remove this solvent and binder materials, the stencil should provide avenues for the solvents to exit. Instead of one big opening over the thermal pad area, the region should be divided into apertures. Figure 7 shows a recommended pattern for the solder stencil. The pattern will let air entrapped in 5 of the 9 vias to out-gas, before reflow occurs. The remaining four holes will out-gas through the solder paste and exit on the sides of the package.

Figure 7: , recommended stencil design

A stencil this thickness of 0.15mm is recommended for the Kinetic QFN devices, which have a 0.65mm lead pitch. Typically, the stencils are laser cut from stainless steel and should be given a slight etch to remove any burrs on the aperture walls. The etch will facilitate the pull-away from the solder. If inspection indicates that too much solder is being applied to the leads, then the pad dimensions on the stencil can be reduced by 20%, with respect to the pads imaged and etched onto the system PCB.

#### **Solder Process**

During reflow, capillary forces will cause the QFN package to naturally align with the circuit pattern on the system board. These same forces will pull the QFN package down to the system PBC. Control of the solder paste thickness is one of the most critical parameters in attaching the QFN package. If too much solder paste is used, it can be squeezed in between the pads and cause bridges and shorts. As indicated above, the package stand-off height is a direct function of the solder paste coverage on the thermal pad and is the best indication whether there is a good connection underneath. Cross sectioning a few of the assemblies is probably the best way to measure the stand-off on a sample basis.

Height adjustment can be achieved by refining the stencil design and screen printing operation. The solder blend, PCB finishes and reflow parameters also impact the stand-off. Some process development will be required to assure that the binder materials out-gas properly and that the bulk of the solder doesn't wick down the thermal vias. Since there is not enough space under the part for cleaning after the reflow process, it is recommended that "no clean" type paste be used for mounting the QFN package. Nitrogen purge is also recommended during reflow. It is best to start with the paste manufacturers' recommended reflow profile, test the joint on multiple parts and then optimize the process settings based on the results.

#### Rework

The QFN parts are light enough that, if misaligned (< 50% off the part center), they will self-align during reflow. Grossly misaligned part need to be removed and re-placed. As with all SMT components, it is important that the IR profiles be checked on all new board designs. The profile should be checked at different locations on the board, since the temperature may vary, depending on the mass and size of surrounding components and package densities.

Reworking QFN packages can be challenging due to their small size and the difficulty of de-soldering the large paddle. During removal, it is recommended that the board be heated from the backside pad, using a soldering iron with a blunt tip. Once the joint reflows, a vacuum pick can be used to lift-off the QFN device from the top surface.

Before replacing the part, the PCB pads must be cleaned. It is best to use a blade-style tip on the soldering iron and braided solder wick. The width of the blade should about the same width as the thermal paddle on the PCB. The soldering iron temperature should be limited so avoid damaging the printed circuit board. Once the residual solder is removed, the pads should be cleaned with a solvent, such as acetone. The solder paste manufacturer will recommend a suitable solvent.

To re-apply the device, solder paste must be applied to the PCB pads. A min-stencil & squeegee can be practical. However in most cases, the solder will need to be applied manually, while observing the part under a microscope. Some bench top re-work stations provide placement tools that will allow the QFN device to be positioned and placed with control of the X and Y and rotational axis. Once the package is placed, the solder should be reflowed with a profile similar to the one used in the original attachment.

#### CONTACT INFORMATION

Kinetic Technologies 6399 San Ignacio Ave, Suite 250, San Jose, CA 95119 USA Tel: (408) 746-9000 Fax: (408) 351-0338 Email inquiries: info@kinet-ic.com Website: http://www.kinet-ic.com

# **Important Notices**

#### Legal Notice

Copyright <sup>©</sup> 2007 Kinetic Technologies. All rights reserved.

Other names, brands and trademarks are the property of others.

Kinetic Technologies assumes no responsibility or liability for information contained in this document. Kinetic reserves the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or services without notice. The information contained herein is believed to be accurate and reliable at the time of printing.

#### **REFERENCE DESIGN POLICY**

This document is provided as a design reference and Kinetic Technologies assumes no responsibility or liability for the information contained in this document. Kinetic reserves the right to make corrections, modifications, enhancements, improvements and other changes to this reference design documentation without notice.

Reference designs are created using Kinetic Technologies's published specifications as well as the published specifications of other device manufacturers. This information may not be current at the time the reference design is built. Kinetic Technologies and/or its licensors do not warrant the accuracy or completeness of the specifications or any information contained therein.

Kinetic does not warrant that the designs are production worthy. Customer should completely validate and test the design implementation to confirm the system functionality for the end use application.

Kinetic Technologies provides its customers with limited product warranties, according to the standard Kinetic Technologies terms and conditions.

For the most current product information visit us at http://www.kinet-ic.com/

#### LIFE SUPPORT POLICY

LIFE SUPPORT: KINETIC' PRODUCTS ARE NOT DESIGNED, INTENDED, OR AUTHORIZED FOR USE AS COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS. NO WARRANTY, EXPRESS OR IMPLIED, IS MADE FOR THIS USE. AUTHORIZATION FOR SUCH USE SHALL NOT BE GIVEN BY KINETIC, AND THE PRODUCTS SHALL NOT BE USED IN SUCH DEVICES OR SYSTEMS, EXCEPT UPON THE WRITTEN APPROVAL OF THE PRESIDENT OF KINETIC FOLLOWING A DETERMINATION BY KINETIC THAT SUCH USE IS FEASIBLE. SUCH APPROVAL MAY BE WITHHELD FOR ANY OR NO REASON.

"Life support devices or systems" are devices or systems which (1) are intended for surgical implant into the human body, (2) support or sustain human life, or (3) monitor critical bodily functions including, but not limited to, cardiac, respirator, and neurological functions, and whose failure to perform can be reasonably expected to result in a significant bodily injury to the user. A "critical component" is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### SUBSTANCE COMPLIANCE

With respect to any representation by Kinetic Technologies that its products are compliant with RoHS, Kinetic Technologies complies with the Restriction of the use of Hazardous Substances Standard ("RoHS"), which is more formally known as Directive 2002/95/EC of the European Parliament and of the Council of 27 January 2003 on the restriction of the use of certain hazardous substances in electrical and electronic equipment. To the best of our knowledge the information is true and correct as of the date of the original publication of the information. Kinetic Technologies bears no responsibility to update such statements.